平成27年度 秋期 応用情報技術者試験問題と解説

問23

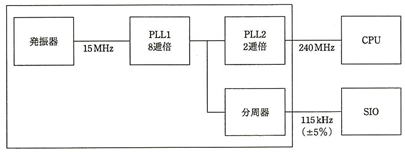

ワンチップマイコンにおける内部クロック発生器のブロック図を示す。15MHzの発振器と、内部のPLL1、PLL2及び分周器の組合せでCPUに240MHz、シリアル通信

(SIO) に115kHzのクロック信号を供給する場合の分周器の値は幾らか。ここで、シリアル通信のクロック精度は±5%以内に収まればよいものとする。

ア 1/24

イ 1/26

ウ 1/28

エ 1/210

正解

エ

解説

発振器から出力された15MHzのクロック信号が、PLL1で8倍され、さらにPLL2で2倍され、CPUに240MHzで供給されている。

SIO には PLL1 で120MHzになった信号を 1/1,024倍すると117kHzとなり、クロック精度±5%以内で115kHzのクロック信号を供給できる。

従って、1/210 となる。

| 問22 | 目次 | 問24 |